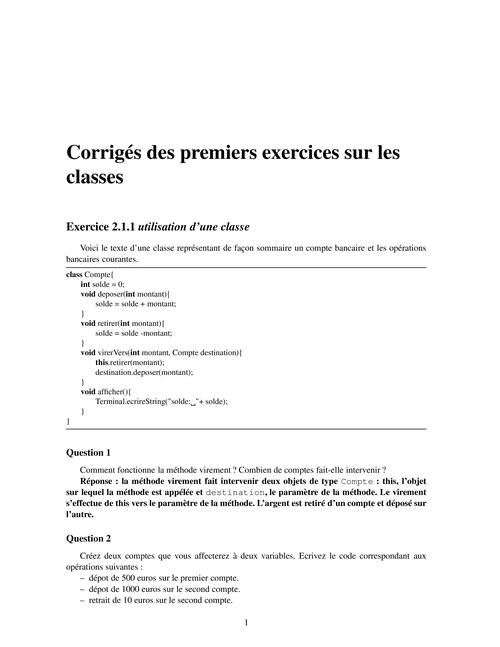

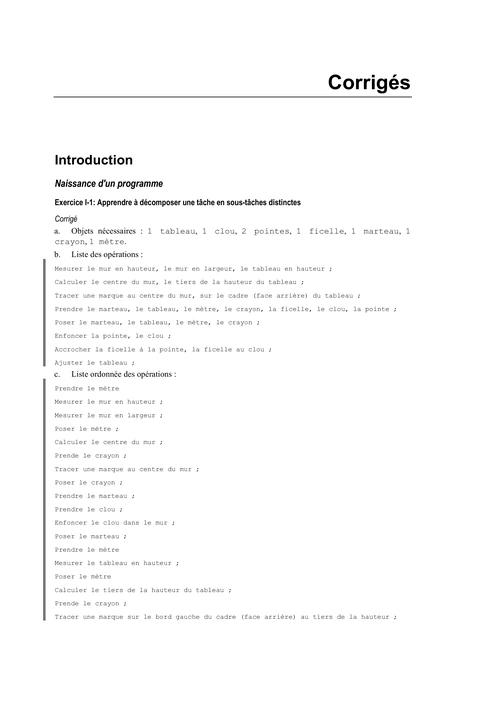

Correction

Module : Conception des circuits intégrés Numériques CMOS. Examen. Exercice 1 (8pts). Soit le transistor nMOS ayant les paramètres suivants : tox=0.1um ...

ES102/PC3 : énoncé et corrigé - ENSTA Paris

Sujet fourni fin-avril/début-mai. ? Discussion à l'examen oral ... Chapitre 1 ? Logique CMOS. ? Logique CMOS ... nécessaire à l'implémentation de l'exercice 1.16 ...

ELEN037 ? Microélectronique

EXERCICE II : II.1 La Figure II, illustre 3 manières différentes pour faire le dessin des masques (layout) d'une paire différentielle.

Conception de Circuits Intégrés Analogique CMOS Master ... - SoC

Exercice. Trouver la forme simplifiée des fonctions à partir des deux tableaux ? ... Exercice 3 : Soit la fonction F ... VLSI (very large) très grande : 10 000 à 99 999.

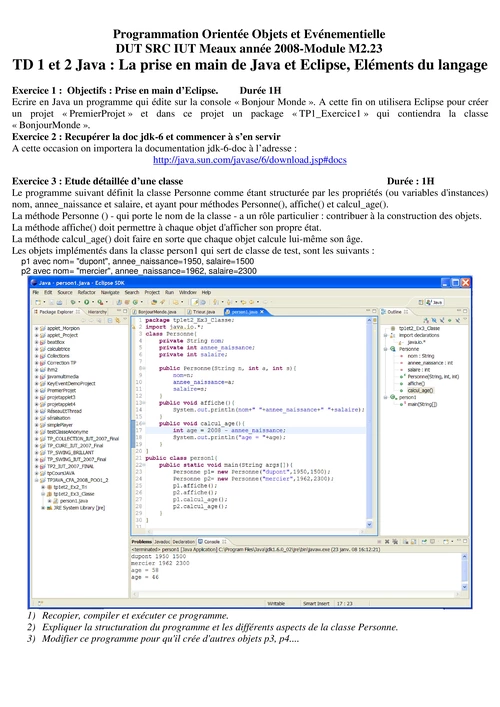

TD1 2007 microélectronique EII2

EXERCICE II : II.1 La Figure II, illustre 3 manières différentes pour faire le dessin des masques (layout) d'une paire différentielle.

Travaux Dirigés Electronique Numérique IUT de Cergy - etis - ensea

Exercice 2 : Donner la fonction logique correspondant au circuit de la figure 1. Exercice 3 : Circuits CMOS. 1) Quelle est la fonction logique correspondant à la ...

corrigé

... les circuits TTL et CMOS...................................................265. 7.4 Interfaces avec les circuits ECL....................................................................266. Exercices corrigés .

Du transistor à la logique CMOS - Mise en perspective

Exercices corrigés. (architecture ordinateurs et circuits logiques). A- Questions de culture générale (non corrigées ici). 1) Comment fonctionne le « tactile » d'une ...

logiques

système de numération et codage exercices corrigés

Exercices corrigés - Pierre Audibert

b) Ecrire ce nombre en binaire en virgule flottante, en simple précision (sur 32 bits). Le résultat obtenu est-il parfaitement exact ? a) 73 s'écrit 1001001. Et pour 0, ...

TD-Technologie des circuits numériques - Free

La logique CMOS utilise les deux types de transistors. La Figure 2 modélise le fonctionnement de l'inverseur CMOS. Les deux états logiques correspondent.

Conservatoire National des Arts et Métiers

Ils se sont aussi livrés à un bref exercice de synthèse des enquêtes ... whereby Japanese negotiators take more time / in order to get to know you well first. C. D.

Exercices avec solutions. (Exercices des TDs et ... - Abdelali ASTITO

Exercices avec solutions : filière EEA ... Manuel des exercices corrigés, anciens examens corrigés ... CC1 d'électronique : parcours GE / GM -S3 (1). Durée = 1h.

CMOS et portes logiques

Une porte logique en CMOS complémentaire est une combinaison de deux réseaux de transistors : un réseau qui branche la sortie `a VDD (PUN : pull-up ...

Support du cours et T Spécialité Support du cours et TD ...

Exercices et Problèmes Corrigés. ? Exercice 1. Soit un CAN tel que sa fréquence d'horloge f= 1MHz, VT =0.1mV, la tension pleine échelle. PE=10,23V et le ...

GELE5340 - Chapitre 5

1.16 Convertisseur numérique analogique (DAC) TD 3.1 opa3-dac ... Corriger le schéma pour rendre ... 4.8 Comportement d'un inverseur CMOS (suite) TD 6.4.

GELE5340 - VLSI - Université de Moncton

Conception de fonctionnalités nouvelles : la technologie VLSI permet ... Exercice. Ecrire le fichier VHDL décrivant la fonction Tranceive permettant une ...

Travaux Dirigés d'Electronique - Enrico Rubiola

11 Electronique télécom et oscillateurs ... Exercice difficile, `a résoudre avec le court circuit virtuel : vd = 0 et i = 0. ... Apr`es avoir corrigé offset et gain, calculer.

Electronique analogique Examen ? Lundi 25 novembre 2019

TD N°1 : transistor bipolaire. Exercice 1. ETUDE STATIQUE ?VB = 0. On choisit VB et RC et RE pour avoir un point de repos VCE0=7.5V. 1. Donner ...